รหัสสินค้า: LISN-PVDC8301

เครือข่ายแหล่งจ่ายไฟ DC เทียมแบบสมมาตร LISN-PVDC8301 ร่วมกับ LISUN EMI-9KB or EMI-9KA สามารถใช้วัดแรงดันไฟฟ้ารบกวนในช่วงความถี่ 0.15 MHz ถึง 30 MHz สำหรับอินเวอร์เตอร์ไฟฟ้าโซลาร์เซลล์ LISN-PVDC8301 ได้รับการออกแบบตาม CISPR 16-1-2 เพื่อวัดการปล่อยก๊าซเรือนกระจกของอินเวอร์เตอร์ไฟฟ้าโซลาร์เซลล์ที่ขั้วจ่ายไฟ แนวคิดวงจรของอินเวอร์เตอร์ไฟฟ้าโซลาร์เซลล์อาจสร้างกระแสกระเพื่อมที่ด้าน DC ของอินเวอร์เตอร์ ซึ่งส่วนใหญ่เป็นสัดส่วนกับความถี่ของกำลัง กระแสกระเพื่อมเหล่านี้สามารถส่งผ่านสายเคเบิลและโมดูลเครื่องกำเนิดไฟฟ้าไฟฟ้าโซลาร์เซลล์ และสามารถทำหน้าที่เป็นรังสีของสนามแม่เหล็ก ซึ่งบางครั้งก่อให้เกิดผลการรบกวนอย่างมีนัยสำคัญ การวัดแบบทั่วไปที่ขั้วไฟฟ้ากระแสสลับของอินเวอร์เตอร์ไฟฟ้าโซลาร์เซลล์ไม่สามารถเปิดเผยปรากฏการณ์การรบกวนดังกล่าวได้ LISN-PVDC8301 ได้รับการออกแบบมาเป็นพิเศษเพื่อวัดแรงดันไฟฟ้ารบกวนทุกชนิดที่ฝั่ง DC ของอินเวอร์เตอร์ไฟฟ้าโซลาร์เซลล์ ต่อไปนี้เป็นรายละเอียดเกี่ยวกับแรงดันไฟฟ้ารบกวนของตัวนำหนึ่งตัวเหนือกราวด์อ้างอิง (แรงดันไฟฟ้ารบกวนแบบไม่สมมาตร) แรงดันไฟฟ้ารบกวนแบบวิธีร่วมของตัวนำคู่หนึ่งเหนือพื้นดิน (แรงดันไฟฟ้ารบกวนแบบอสมมาตร) และสุดท้ายคือแรงดันไฟฟ้าโหมดดิฟเฟอเรนเชียลระหว่างตัวนำสองตัว

ข้อมูลจำเพาะ:

| ช่วงความถี่ | 0.15 เมกะเฮิรตซ์ - 30 เมกะเฮิรตซ์ |

| กระแสสูงสุด (DC) | 200 |

| แรงดันไฟฟ้าสูงสุด (DC) | V 1500 |

| ความต้านทานโหมดทั่วไป | (150 +/- 30) โอห์ม |

| (สวิตช์โหมด CM, A หรือ B) | |

| ความต้านทานโหมดดิฟเฟอเรนเชียล | (150 +/- 30) โอห์ม |

| (สวิตช์โหมด DM) | |

| เฟสที่ EUT-Terminals | (0 +/- 40)° |

| การสูญเสียการแทรก (EUT – AE) | > 20 dB |

| LCL การสูญเสียการแปลงตามยาว | > 26 dB |

| ปัจจัยการแบ่งแรงดันที่พอร์ตการวัด | ประเภท (20 +/- 3) เดซิเบล (10:1) |

| ความต้านทาน (DC) เมื่อขั้วต่อฟีดลัดวงจร (T=25°C) | <50 ม |

| ขั้วต่อ EUT | ขั้วต่อ M12 พร้อมช่องเสียบแบนเนอร์ |

| ขนาด | 42 * * * * * * * * 28 44 ซม. |

| น้ำหนัก | ประมาณ 33 กก. |

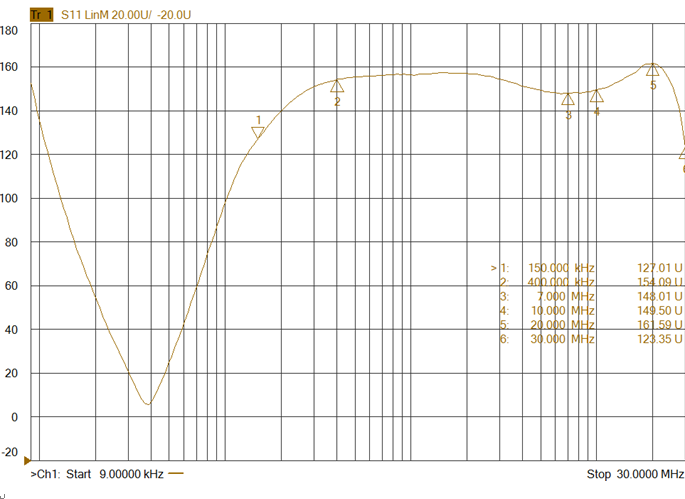

รูปที่ 1 ความต้านทานโหมดร่วม

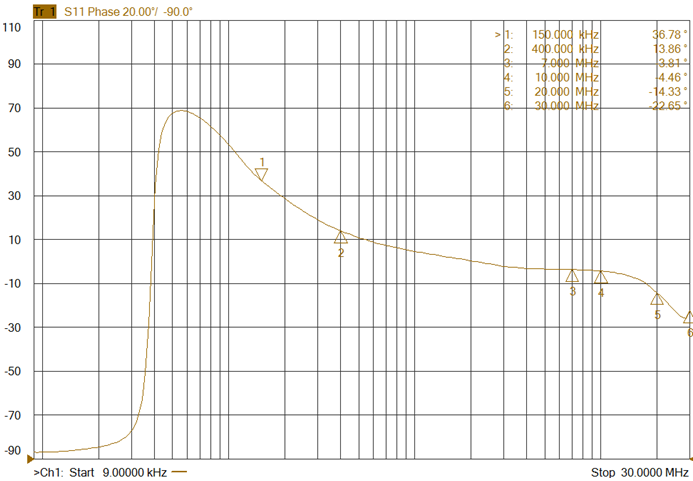

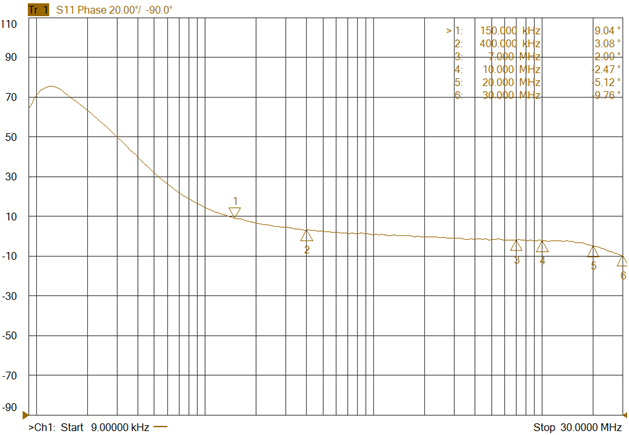

รูปที่ 2 แผนภาพเฟสโหมดทั่วไป

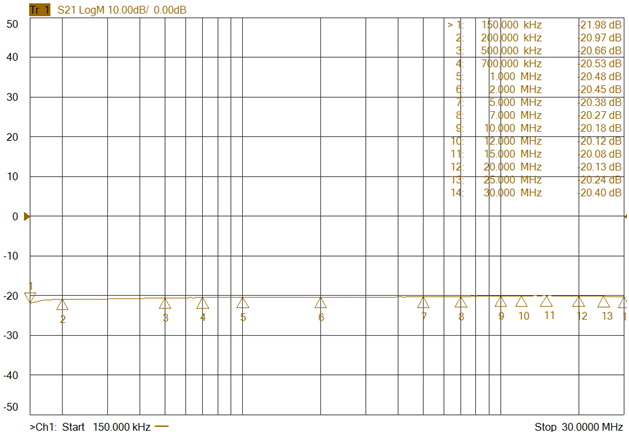

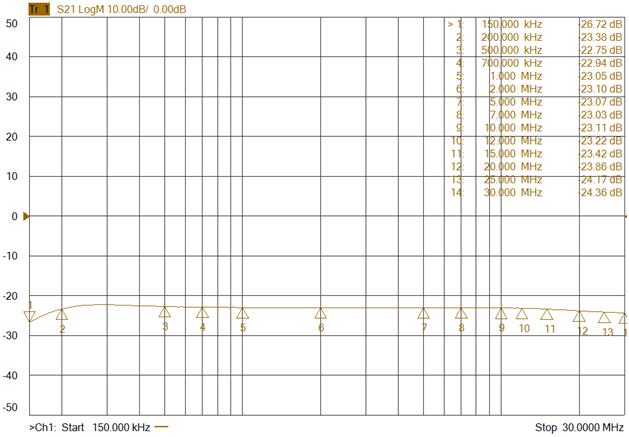

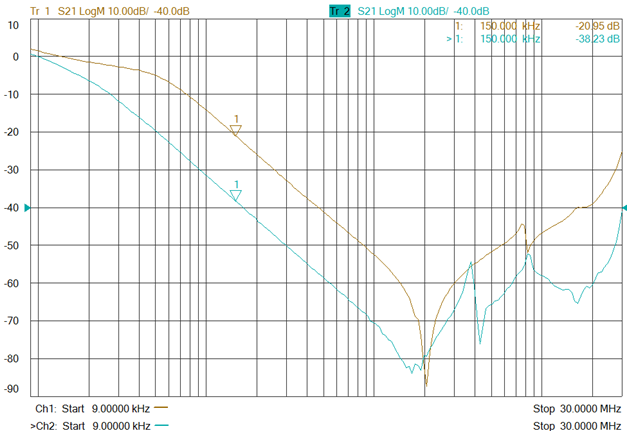

รูปที่ 3: แผนภาพค่าสัมประสิทธิ์การลดทอนของ C-end (โหมดทั่วไป)

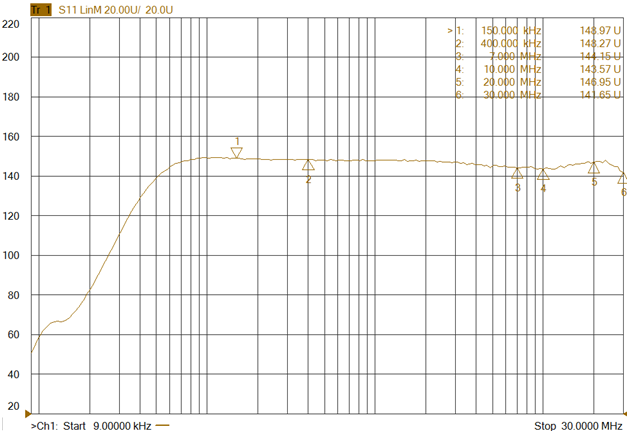

รูปที่ 4: แผนภาพความต้านทาน D-end (โหมดดิฟเฟอเรนเชียล)

รูปที่ 5: แผนภาพเฟส D-end (โหมดดิฟเฟอเรนเชียล)

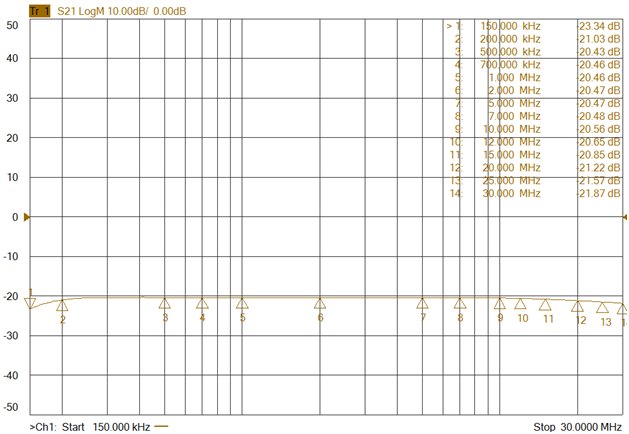

รูปที่ 6: แผนภาพค่าสัมประสิทธิ์การลดทอน D-end (โหมดดิฟเฟอเรนเชียล)

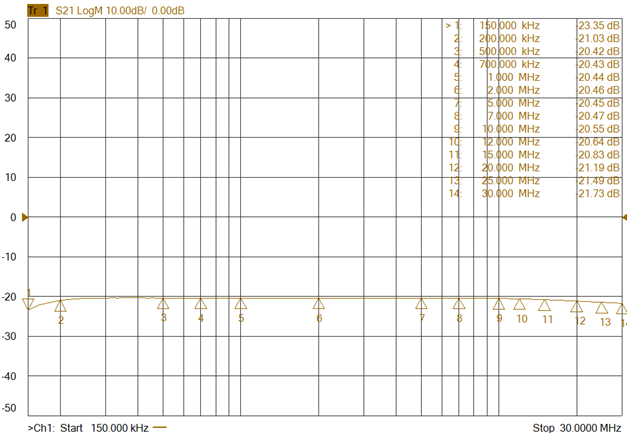

รูปที่ 7: แผนภาพค่าสัมประสิทธิ์การลดทอน A-end

รูปที่ 8: แผนภาพค่าสัมประสิทธิ์การลดทอน B-end

รูปที่ 9: แผนภาพค่าสัมประสิทธิ์การลดทอน B-end